# Quad IEEE 802.3af Power over Ethernet Controller with Integrated Detection

## **FEATURES**

- Controls Four Independent 48V Powered Ethernet Ports

- Each Port Includes:

- IEEE 802<sup>®</sup>.3af Compliant PD Detection and Classification

- Output Current Limit with Foldback

- Short-Circuit Protection with Fast Gate Pull-Down

- PD Disconnect Using DC Sensing

- Power Good Indication

- Operates Autonomously or Controlled by I<sup>2</sup>C<sup>TM</sup> Serial Interface

- 4-Bit Programmable Digital Address Allows Control of Up to 64 Ports

- Programmable INT Pin Eliminates Software Polling

- Current and Duty Cycle Limits Protect External FETs

## **APPLICATIONS**

- IEEE 802.3af Compliant Endpoint and Midspan Power Sources

- IP Phone Systems

- DTE Power Distribution

**47**, LTC and LT are registered trademarks of Linear Technology Corporation. Hot Swap is a trademark of Linear Technology Corporation. 802 is a registered trademark of Instutute of Electrical and Electronics Engineers, Inc. |<sup>2</sup>C is a trademark of Philips Electronics N.V.

#### DESCRIPTION

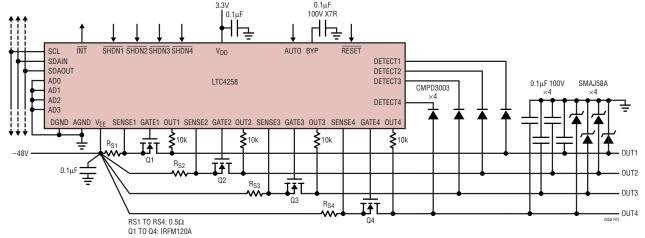

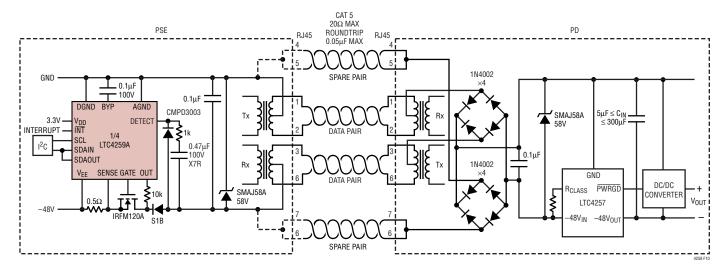

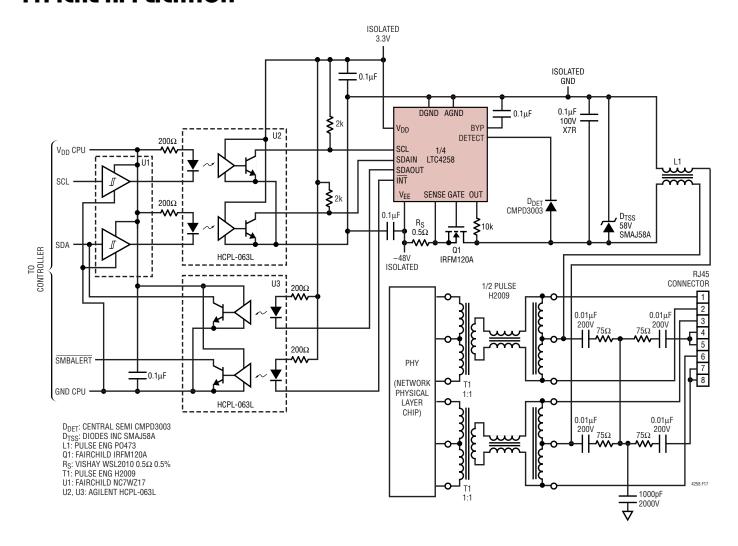

The LTC®4258 is a quad −48V Hot Swap™ controller designed for use in IEEE 802.3af compliant Power Sourcing Equipment (PSE). It consists of four independent ports, each with output current limit, short-circuit protection, complete Powered Device (PD) detection and classification capability, and programmable PD disconnect using AC or DC sensing. Used with power MOSFETs and passives as in Figure 1, the LTC4258 can implement a complete IEEE 802.3af-compliant PSE.

The LTC4258 can operate autonomously or be controlled by an  $I^2C$  serial interface. Up to 16 LTC4258s may coexist on the same data bus, allowing up to 64 powered Ethernet ports to be controlled with only two digital lines. Fault conditions are optionally signaled with the  $\overline{INT}$  pin to eliminate software polling.

External power MOSFETs, current sense resistors and diodes allow easy scaling of current and power dissipation levels and provide protection against voltage and current spikes and ESD events.

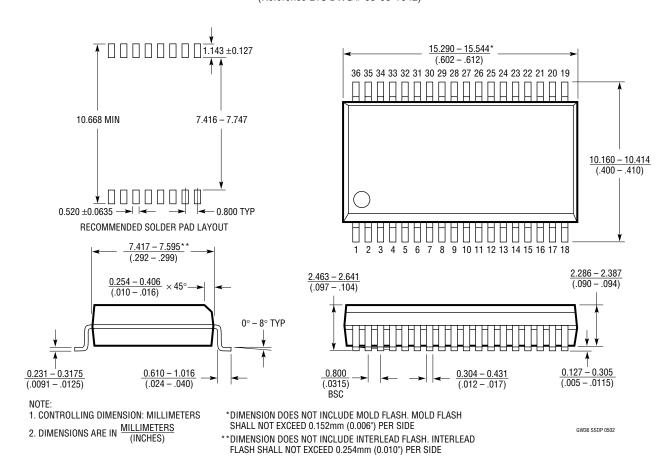

The LTC4258 is available in a 36-pin SSOP package.

Linear Technology also provides solutions for 802.3af PD applications with the LTC4257 and LTC4257-1.

## TYPICAL APPLICATION

Figure 1. Complete 4-Port Powered Ethernet Power Source

## **ABSOLUTE MAXIMUM RATINGS**

## (Note 1) Supply Voltages $V_{DD}$ to DGND ...... -0.3V to 5VV<sub>EE</sub> to AGND ...... 0.3V to -70V DGND to AGND (Note 2) ..... ±1V **Digital Pins** SCL, SDAIN, SDAOUT, INT, AUTO, RESET Analog Pins $\overline{\text{GATE}}n$ (Note 3) ...... $V_{\text{EE}} - 0.3 \text{V}$ to $V_{\text{EE}} + 12 \text{V}$ DETECT*n* ...... DGND –20V to DGND +0.3V SENSE*n* ...... $V_{FF} - 0.3V$ to $V_{FF} + 1V$ OSCIN ...... DGND - 0.3V to DGND + 5V BYP Current ..... ±0.1mA Operating Ambient Temperature Range ..... 0°C to 70°C Junction Temperature (Note 5) ...... 150°C Storage Temperature Range ...... -65°C to 150°C Lead Temperature (Soldering, 10 sec)............... 300°C

## PACKAGE/ORDER INFORMATION

|                 | TOP VIEW                               | <b>L</b> _         | ORDER PART  |

|-----------------|----------------------------------------|--------------------|-------------|

| RESET           | 1                                      | 36 NC              | NUMBER      |

| ВҮР             | 2                                      | 35 AUTO            |             |

| ĪNT             | 3                                      | 34 OUT1            | LTC4258CGW  |

| SCL             | 4                                      | 33 GATE1           | L10423000VV |

| SDAOUT          | 5                                      | 32 SENSE1          |             |

| SDAIN           | 6                                      | 31 OUT2            |             |

| AD3             | 7                                      | 30 GATE2           |             |

| AD2             | 8                                      | 29 SENSE2          |             |

| AD1             | 9                                      | 28 V <sub>EE</sub> |             |

| AD0             | 10                                     | 27 OUT3            |             |

| DETECT1         | 11                                     | 26 GATE3           |             |

| DETECT2         | 12                                     | 25 SENSE3          |             |

| DETECT3         | 13                                     | 24 OUT4            |             |

| DETECT4         | 14                                     | 23 GATE4           |             |

| DGND            | 15                                     | 22 SENSE4          |             |

| $V_{DD}$        | 16                                     | 21 AGND            |             |

| SHDN1           | 17                                     | 20 SHDN4           |             |

| SHDN2           | 18                                     | 19 SHDN3           |             |

|                 | GW PACKAGE<br>36-LEAD PLASTIC S        | -<br>SOP           |             |

| T <sub>JM</sub> | $_{AX} = 150^{\circ}C,  \theta_{JA} =$ | 80°C/W             |             |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . AGND = DGND = 0V,  $V_{DD} = 3.3V$ ,  $V_{EE} = -48V$  unless otherwise noted (Note 5).

| SYMBOL                | PARAMETER                                  | CONDITIONS                                                                   |   | MIN        | TYP | MAX        | UNITS    |

|-----------------------|--------------------------------------------|------------------------------------------------------------------------------|---|------------|-----|------------|----------|

| Power Sup             | plies                                      |                                                                              |   |            |     |            |          |

| $V_{DD}$              | V <sub>DD</sub> Supply Voltage             |                                                                              | • | 3          | 3.3 | 4          | V        |

| V <sub>EE</sub>       | V <sub>EE</sub> Supply Voltage             | To Maintain IEEE Compliant Output (Note 6)                                   | • | -48        |     | -57        | V        |

| $I_{DD}$              | V <sub>DD</sub> Supply Current             |                                                                              | • |            | 2.5 | 5          | mA       |

| I <sub>EE</sub>       | V <sub>EE</sub> Supply Current             | Normal Operation During Classification Into Short (V <sub>DETECT</sub> = 0V) | • |            | -2  | -5<br>85   | mA<br>mA |

| $V_{\rm DDMIN}$       | V <sub>DD</sub> UVLO Voltage               |                                                                              |   |            | 2.7 |            | V        |

| V <sub>EEMINON</sub>  | V <sub>EE</sub> UVLO Voltage (Turning On)  | V <sub>EE</sub> – AGND                                                       |   |            | -31 |            | V        |

| V <sub>EEMINOFF</sub> | V <sub>EE</sub> UVLO Voltage (Turning Off) | V <sub>EE</sub> – AGND                                                       |   |            | -28 |            | V        |

| Detection             |                                            |                                                                              |   |            |     |            |          |

| I <sub>DET</sub>      | Detection Current                          | First Point, $V_{DETECT} = -10V$<br>Second Point, $V_{DETECT} = -3.5V$       | • | 235<br>145 |     | 300<br>190 | μA<br>μA |

| $V_{DET}$             | Detection Voltage Compliance               | Open Circuit, Measured at DETECT <i>n</i> Pin                                | • |            | -20 | -23        | V        |

| R <sub>DETMIN</sub>   | Minimum Valid Signature Resistance         |                                                                              | • | 15.2       | 17  | 19         | kΩ       |

| R <sub>DETMAX</sub>   | Maximum Valid Signature Resistance         |                                                                              | • | 26.7       | 29  | 33         | kΩ       |

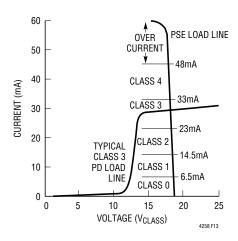

| Classificat           | ion                                        |                                                                              |   |            |     |            |          |

| V <sub>CLASS</sub>    | Classification Voltage                     | 0mA < I <sub>CLASS</sub> < 31mA                                              | • | -16.4      |     | -21        | V        |

| I <sub>CLASS</sub>    | Classification Current Compliance          | Into Short (V <sub>DETECT</sub> = 0V)                                        | • | 55         |     | 75         | mA       |

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . AGND = DGND = 0V, $V_{DD} = 3.3V$ , $V_{EE} = -48V$ unless otherwise noted (Note 5).

| SYMBOL              | PARAMETER                                                      | CONDITIONS                                                                                                                |   | MIN      | TYP      | MAX      | UNITS    |

|---------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---|----------|----------|----------|----------|

| I <sub>TCLASS</sub> | Classification Threshold Current                               | Class 0-1                                                                                                                 | • | 5.5      | 6.5      | 7.5      | mA       |

|                     |                                                                | Class 1-2                                                                                                                 | • | 13       | 14.5     | 16       | mA       |

|                     |                                                                | Class 2-3<br>Class 3-4                                                                                                    | • | 21       | 23       | 25       | mA       |

|                     |                                                                | Class 4-Overcurrent                                                                                                       |   | 31<br>45 | 33<br>48 | 35<br>51 | mA<br>mA |

| Gate Drive          | r                                                              | Glass 4-Overcurrent                                                                                                       |   | 40       | 40       | - 01     | 1117     |

| I <sub>GON</sub>    | GATE Pin Current                                               | Gate On, V <sub>GATEn</sub> = V <sub>EE</sub>                                                                             |   | -20      | -50      | -70      | μА       |

| I <sub>GOFF</sub>   | GATE Pin Current                                               | Gate Off, V <sub>GATE</sub> , = V <sub>EE</sub> + 5V                                                                      | • | 30       | 50       | 95       | μΑ       |

| I <sub>GPD</sub>    | GATE Pin Short-Circuit Pull-Down                               | V <sub>GATE</sub> , = V <sub>EE</sub> + 5V                                                                                |   |          | 100      |          | mA       |

| ΔV <sub>GATE</sub>  | External Gate Voltage (V <sub>GATE</sub> n – V <sub>EE</sub> ) | $I_{GATE} = -1\mu A \text{ (Note 3)}$                                                                                     |   | 10       | 13       | 15       | V        |

|                     | tage Sense                                                     | IGATE - TEXT (NOTE O)                                                                                                     |   | 10       | 10       | 10       | V        |

| V <sub>PG</sub>     | Power Good Threshold Voltage                                   | $V_{OUT} - V_{EE}$                                                                                                        | • | 1        | 2        | 3        | V        |

| I <sub>VOUT</sub>   | Out Pin Bias Current                                           | 0V > V <sub>OUT</sub> > -10V                                                                                              | • | •        |          |          | μА       |

| 10001               | Out i iii bias ourront                                         | -10V > V <sub>OUT</sub> > -30V                                                                                            | • |          |          | -18      | μΑ       |

|                     |                                                                | $V_{OUT} = -48V$                                                                                                          |   |          | -20      |          | μA       |

| <b>Current Se</b>   | ense                                                           |                                                                                                                           |   |          |          |          |          |

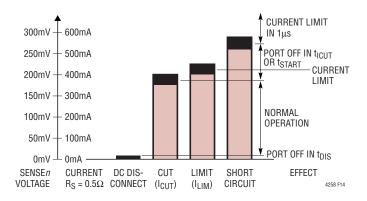

| V <sub>CUT</sub>    | Overcurrent Detection Sense Voltage                            | $V_{SENSE} - V_{EE}, V_{OUT} = V_{EE} $ (Note 7)                                                                          |   | 166      | 187.5    | 199      | mV       |

| $V_{LIM}$           | Current Limit Sense Voltage                                    | $V_{SENSE} - V_{EE}, V_{OUT} = V_{EE}$                                                                                    |   | 201      | 212.5    | 224      | mV       |

|                     |                                                                | $V_{SENSE} - V_{EE}, V_{OUT} = AGND - 30V$                                                                                |   | 201      |          | 224      | mV       |

|                     |                                                                | $V_{SENSE} - V_{EE}$ , $V_{OUT} = AGND - 10V$                                                                             |   | 30.2     |          |          | mV       |

| V <sub>MIN</sub>    | DC Disconnect Sense Voltage                                    | V <sub>SENSE</sub> n – V <sub>EE</sub>                                                                                    |   | 2.52     | 3.75     | 4.97     | mV       |

| V <sub>SC</sub>     | Short-Circuit Sense Voltage                                    |                                                                                                                           |   |          | 275      |          | mV       |

| I <sub>SENSE</sub>  | SENSE Pin Bias Current                                         | $V_{SENSE} = V_{EE}$                                                                                                      |   |          | -50      |          | μΑ       |

| Digital Int         | 1                                                              |                                                                                                                           |   |          |          |          |          |

| $V_{OLD}$           | Digital Output Low Voltage                                     | I <sub>SDAOUT</sub> = 3mA, I <sub>INT</sub> = 3mA                                                                         | • |          |          | 0.4      | V        |

|                     | B: 211                                                         | I <sub>SDAOUT</sub> = 5mA, I <sub>INT</sub> = 5mA                                                                         | • |          |          | 0.7      | V        |

| $V_{ILD}$           | Digital Input Low Voltage                                      | SCL, SDAIN, RESET, SHDNn, AUTO                                                                                            | • |          |          | 0.8      | V        |

| V <sub>IHD</sub>    | Digital Input High Voltage                                     | SCL, SDAIN, RESET, SHDNn, AUTO                                                                                            | • | 2.4      |          |          | V        |

| R <sub>PU</sub>     | Pull-Up Resistor to V <sub>DD</sub>                            | AD0 to AD3, RESET, SHDNn                                                                                                  |   |          | 50       |          | kΩ       |

| R <sub>PD</sub>     | Pull-Down Resistor to DGND                                     | AUTO                                                                                                                      |   |          | 50       |          | kΩ       |

| AC Charac           | teristics                                                      |                                                                                                                           |   |          |          |          |          |

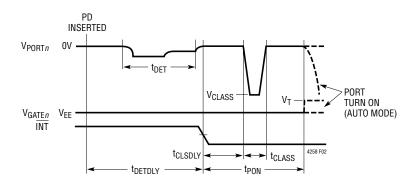

| t <sub>DETDLY</sub> | Detection Delay                                                | From Detect Command or Application of PD to Port to Detect Complete                                                       | • | 170      |          | 590      | ms       |

| t <sub>DET</sub>    | Detection Duration                                             | Time to Measure PD Signature Resistance (Figure 2)                                                                        | • | 170      |          | 230      | ms       |

| t <sub>CLSDLY</sub> | Classification Delay                                           | From Successful Detect in Auto or Semiauto Mode                                                                           | • | 10.1     |          | 52       | ms       |

|                     |                                                                | to Class Complete                                                                                                         |   | 10.1     |          | 400      | m.       |

| +                   | Classification Duration                                        | From Classify Command in Manual                                                                                           |   | 10.1     |          | 420      | ms       |

| t <sub>CLASS</sub>  | Classification Duration                                        | (Figure 2)                                                                                                                | • | 10.1     |          | 13       | ms       |

| t <sub>PON</sub>    | Power On Delay, Auto Mode                                      | From Valid Detect to Port On in Auto Mode (Figure 2) From Port On Command to GATE Pin Current = I <sub>GON</sub> (Note 8) | • |          |          | 90<br>1  | ms<br>ms |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . AGND = DGND = 0V,  $V_{DD} = 3.3V$ ,  $V_{EE} = -48V$  unless otherwise noted (Note 5).

| SYMBOL                  | PARAMETER                                              | CONDITIONS                                                                                                                                                                                                              |   | MIN                     | TYP                     | MAX                      | UNITS                |

|-------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------|-------------------------|--------------------------|----------------------|

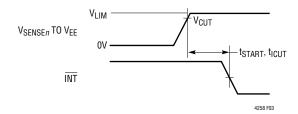

| t <sub>START</sub>      | Maximum Current Limit Duration During<br>Port Start-Up | t <sub>START1</sub> = 0, t <sub>START0</sub> = 0 (Figure 3)<br>t <sub>START1</sub> = 0, t <sub>START0</sub> = 1<br>t <sub>START1</sub> = 1, t <sub>START0</sub> = 0<br>t <sub>START1</sub> = 1, t <sub>START0</sub> = 1 | • | 50<br>25<br>100<br>200  | 60<br>30<br>120<br>240  | 70<br>35<br>140<br>280   | ms<br>ms<br>ms<br>ms |

| t <sub>ICUT</sub>       | Maximum Current Limit Duration After<br>Port Start-Up  | t <sub>ICUT1</sub> = 0, t <sub>ICUT0</sub> = 0 (Figure 3)<br>t <sub>ICUT1</sub> = 0, t <sub>ICUT0</sub> = 1<br>t <sub>ICUT1</sub> = 1, t <sub>ICUT0</sub> = 0<br>t <sub>ICUT1</sub> = 1, t <sub>ICUT0</sub> = 1         | • | 50<br>25<br>100<br>200  | 60<br>30<br>120<br>240  | 70<br>35<br>140<br>280   | ms<br>ms<br>ms<br>ms |

| DC <sub>CLMAX</sub>     | Maximum Current Limit Duty Cycle                       | Reg16h = 00h                                                                                                                                                                                                            | • | 5.8                     | 6.3                     | 6.7                      | %                    |

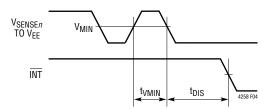

| t <sub>DIS</sub>        | Disconnect Delay                                       | t <sub>DIS1</sub> = 0, t <sub>DIS0</sub> = 0 (Figure 4)<br>t <sub>DIS1</sub> = 0, t <sub>DIS0</sub> = 1<br>t <sub>DIS1</sub> = 1, t <sub>DIS0</sub> = 0<br>t <sub>DIS1</sub> = 1, t <sub>DIS0</sub> = 1                 | • | 300<br>75<br>150<br>600 | 360<br>90<br>180<br>720 | 400<br>100<br>200<br>800 | ms<br>ms<br>ms       |

| t <sub>VMIN</sub>       | DC Disconnect Minimum Pulse<br>Width Sensitivity       | $V_{SENSE} - V_{EE} > 5 \text{mV}, V_{OUT} = -48 \text{V (Figure 4)}$<br>(Note 8)                                                                                                                                       | • |                         | 0.02                    | 1                        | ms                   |

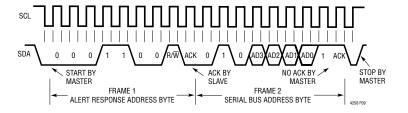

| I <sup>2</sup> C Timing |                                                        |                                                                                                                                                                                                                         |   |                         |                         |                          |                      |

| f <sub>SCLK</sub>       | Clock Frequency                                        | (Note 8)                                                                                                                                                                                                                | • |                         |                         | 400                      | kHz                  |

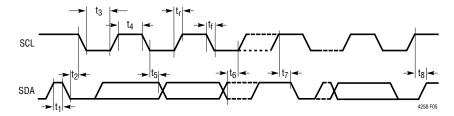

| t <sub>1</sub>          | Bus Free Time                                          | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 1.3                     |                         |                          | μs                   |

| t <sub>2</sub>          | Start Hold Time                                        | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 600                     |                         |                          | ns                   |

| $t_3$                   | SCL Low Time                                           | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 1.3                     |                         |                          | μS                   |

| t <sub>4</sub>          | SCL High Time                                          | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 600                     |                         |                          | ns                   |

| t <sub>5</sub>          | Data Hold Time                                         | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 150                     |                         |                          | ns                   |

| t <sub>6</sub>          | Data Set-Up Time                                       | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 200                     |                         |                          | ns                   |

| t <sub>7</sub>          | Start Set-Up Time                                      | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 600                     |                         |                          | ns                   |

| t <sub>8</sub>          | Stop Set-Up Time                                       | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 600                     |                         |                          | ns                   |

| t <sub>r</sub>          | SCL, SDAIN Rise Time                                   | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 20                      |                         | 300                      | ns                   |

| tf                      | SCL, SDAIN Fall Time                                   | Figure 5 (Notes 8, 9)                                                                                                                                                                                                   | • | 20                      |                         | 150                      | ns                   |

| t <sub>FLTINT</sub>     | Fault Present to INT Pin Low                           | (Notes 8, 9, 10)                                                                                                                                                                                                        | • | 20                      |                         | 150                      | ns                   |

| t <sub>STOPINT</sub>    | Stop Condition to INT Pin Low                          | (Notes 8, 9, 10)                                                                                                                                                                                                        | • | 60                      |                         | 200                      | ns                   |

| t <sub>ARAINT</sub>     | ARA to INT Pin High Time                               | (Notes 8, 9)                                                                                                                                                                                                            | • | 20                      |                         | 300                      | ns                   |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

**Note 2:** DGND and AGND should be tied together in normal operation.

**Note 3:** An internal clamp limits the GATE pins to a minimum of 12V above  $V_{\text{EE}}$ . Driving this pin beyond the clamp may damage the part.

**Note 4:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 5:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground (AGND and DGND) unless otherwise specified.

**Note 6:** The LTC4258 is designed to maintain a port voltage of -46.6V to -57V and the V<sub>EE</sub> supply voltage range accounts for the drop across the diode, MOSFET and sense resistor.

**Note 7:** The LTC4258 implements overload current detection per IEEE 802.3af. The minimum overload current (I<sub>CUT</sub>) is dependent on port voltage; I<sub>CUT\_MIN</sub> = 15.4W/V<sub>PORT\_MIN</sub>. An IEEE compliant system using the LTC4258 should maintain port voltage above –46.6V.

Note 8: Guaranteed by design, not subject to test.

Note 9: Values measured at  $V_{ILD}$  and  $V_{IHD}$ .

**Note 10:** If fault occurs during an  $I^2C$  transaction, the  $\overline{INT}$  pin will not be pulled down until a stop condition is present on the  $I^2C$  bus.

TECHNOLOGY TECHNOLOGY

## **TEST TIMING**

Figure 2. Detect, Class and Turn-On Timing in Auto or Semiauto Modes

Figure 3. Current Limit Timing

Figure 4. DC Disconnect Timing

Figure 5. I<sup>2</sup>C Interface Timing

## TIMING DIAGRAMS

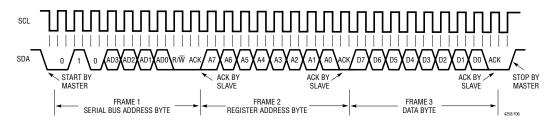

Figure 6. Writing to a Register

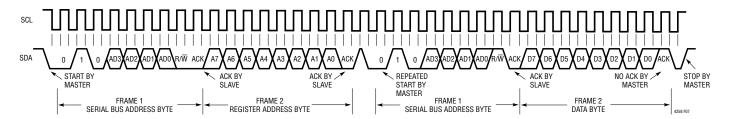

Figure 7. Reading from a Register

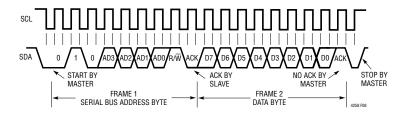

Figure 8. Reading the Interrupt Register (Short Form)

Figure 9. Reading from Alert Response Address

## PIN FUNCTIONS

**RESET (Pin 1):** Chip Reset, Active Low. When the RESET pin is low, the LTC4258 is held inactive with all ports off and all internal registers reset to their power-up states. When  $\overline{RESET}$  is pulled high, the LTC4258 begins normal operation. RESET can be connected to an external capacitor or RC network to provide a power turn-on delay. Internal filtering of the  $\overline{RESET}$  pin prevents glitches less than  $1\mu s$  wide from resetting the LTC4258. Pull  $\overline{RESET}$  high with  $\leq 10k$  or tie to  $V_{DD}$ .

**BYP** (**Pin 2**): Bypass Output. The BYP pin is used to connect the internally generated -20V supply to an external  $0.1\mu F$  bypass capacitor. Use a 100V rated  $0.1\mu F$ , X7R capacitor. Do not connect the BYP pin to any other external circuitry.

INT (Pin 3): Interrupt Output, Open Drain. INT will pull low when any one of several events occur in the LTC4258. It will return to a high impedance state when bits 6 or 7 are set in the Reset PB register (1Ah). The INT signal can be used to generate an interrupt to the host processor, eliminating the need for continuous software polling. Individual INT events can be disabled using the Int Mask register (01h). See Register Functions and Applications Information for more information. The INT pin is only updated between I<sup>2</sup>C transactions.

**SCL** (**Pin 4**): Serial Clock Input. High impedance clock input for the I<sup>2</sup>C serial interface bus. The SCL pin should be connected directly to the I<sup>2</sup>C SCL bus line.

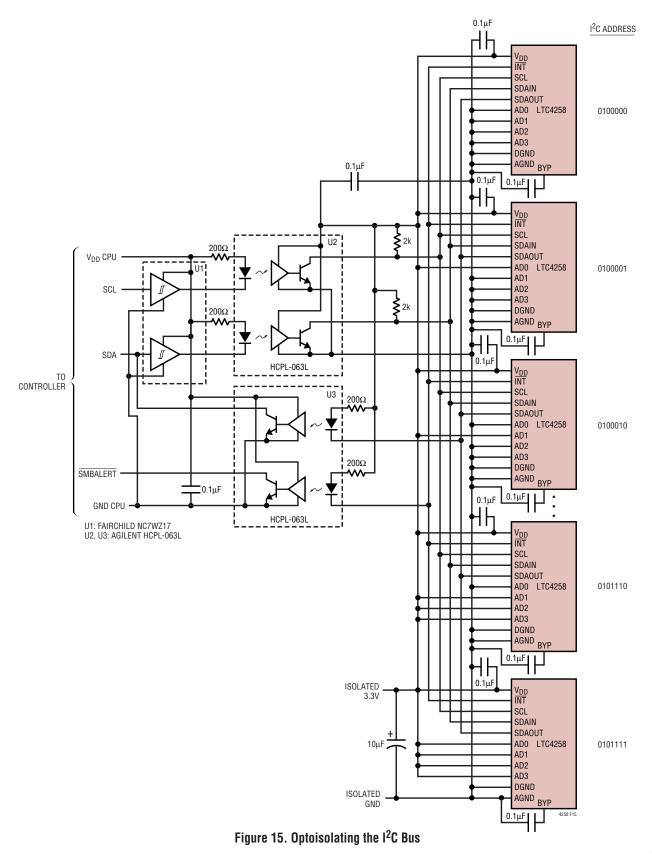

**SDAOUT (Pin 5):** Serial Data Output, Open Drain Data Output for the I<sup>2</sup>C Serial Interface Bus. The LTC4258 uses two pins to implement the bidirectional SDA function to simplify optoisolation of the I<sup>2</sup>C bus. To implement a standard bidirectional SDA pin, tie SDAOUT and SDAIN together. See Applications Information for more information.

**SDAIN (Pin 6):** Serial Data Input. High impedance data input for the  $I^2C$  serial interface bus. The LTC4258 uses two pins to implement the bidirectional SDA function to simplify optoisolation of the  $I^2C$  bus. To implement a standard bidirectional SDA pin, tie SDAOUT and SDAIN together. See Applications Information for more information.

**AD3 (Pin 7):** Address Bit 3. Tie the address pins high or low to set the  $I^2C$  serial address to which the LTC4258 responds. This address will be  $(010A_3A_2A_1A_0)_b$ . Pull AD3 high or low with  $\leq 10k$  or tie to  $V_{DD}$  or DGND.

AD2 (Pin 8): Address Bit 2. See AD3.

AD1 (Pin 9): Address Bit 1. See AD3.

ADO (Pin 10): Address Bit O. See AD3.

**DETECT1 (Pin 11):** Detect Sense, Port 1. The LTC4258 Powered Device (PD) detection, classification and AC disconnect hardware monitors port 1 with this pin. Connect DETECT1 to the output port via a low leakage diode (see Figure 1).

**DETECT2 (Pin 12):** Detection Sense, Port 2. See DETECT1.

**DETECT3 (Pin 13):** Detection Sense, Port 3. See DETECT1.

**DETECT4 (Pin 14):** Detection Sense, Port 4. See DETECT1.

**DGND (Pin 15):** Digital Ground. DGND should be connected to the return from the 3.3V supply. DGND and AGND should be tied together.

$V_{DD}$  (Pin 16): Logic Power Supply. Connect to a 3.3V power supply relative to DGND.  $V_{DD}$  must be bypassed to DGND near the LTC4258 with at least a 0.1 $\mu$ F capacitor.

**SHDN1 (Pin 17):** Shutdown Port 1, Active Low. When pulled low,  $\overline{SHDN1}$  shuts down port 1, regardless of the state of the internal registers. Pulling  $\overline{SHDN1}$  low is equivalent to setting the Reset Port 1 bit in the Reset Pushbutton register (1Ah). Internal filtering of the  $\overline{SHDN1}$  pin prevents glitches less than 1 $\mu$ s wide from reseting the LTC4258. Pull  $\overline{SHDN1}$  high with  $\leq$ 10k or tie to  $\overline{V_{DD}}$ .

**SHDN2 (Pin 18):** Shutdown Port 2, Active Low. See SHDN1.

SHDN3 (Pin 19): Shutdown Port 3, Active Low. See SHDN1.

SHDN4 (Pin 20): Shutdown Port 4, Active Low. See SHDN1.

## PIN FUNCTIONS

**AGND (Pin 21):** Analog Ground. AGND should be connected to the return from the -48V supply. AGND and DGND should be tied together.

**SENSE4** (**Pin 22**): Port 4 Current Sense Input. SENSE4 monitors the external MOSFET current via a  $0.5\Omega$  sense resistor between SENSE4 and  $V_{EE}$ . Whenever the voltage across the sense resistor exceeds the overcurrent detection threshold  $V_{CUT}$ , the current limit fault timer counts up. If the voltage across the sense resistor reaches the current limit threshold  $V_{LIM}$  (typically 25mV/50mA higher), the GATE4 pin voltage is lowered to maintain constant current in the external MOSFET. See Applications Information for further details. If the port is unused, the SENSE4 pin must be tied to  $V_{FE}$ .

**GATE4 (Pin 23):** Port 4 Gate Drive. GATE4 should be connected to the gate of the external MOSFET for port 4. When the MOSFET is turned on, a  $50\mu$ A pull-up current source is connected to the pin. The gate voltage is clamped to 13V (typ) above  $V_{EE}$ . During a current limit condition, the voltage at GATE4 will be reduced to maintain constant current through the external MOSFET. If the fault timer expires, GATE4 is pulled down with  $50\mu$ A, turning the MOSFET off and recording a  $t_{ICUT}$  or  $t_{START}$  event. If the port is unused, float the GATE4 pin or tie it to  $V_{FE}$ .

**OUT4** (**Pin 24**): Port 4 Output Voltage Monitor. OUT4 should be connected to the output port through a 10k series resistor. A current limit foldback circuit limits the power dissipation in the external MOSFET by reducing the current limit threshold when the port voltage is within 18V of AGND. The port 4 Power Good bit is set when the voltage

from OUT4 to V<sub>EE</sub> drops below 2V (typ). A 2.5M $\Omega$  resistor is connected internally from OUT4 to AGND. If the port is unused, the OUT4 pin can be tied to AGND or allowed to float.

SENSE3 (Pin 25): Port 3 Current Sense Input. See SENSE4.

GATE3 (Pin 26): Port 3 Gate Drive. See GATE4.

**OUT3 (Pin 27):** Port 3 Output Voltage Monitor. See OUT4.

$V_{EE}$  (Pin 28): -48V Supply Input. Connect to a -48V to -57V supply, relative to AGND.

SENSE2 (Pin 29): Port 2 Current Sense Input. See SENSE4.

GATE2 (Pin 30): Port 2 Gate Drive. See GATE4.

OUT2 (Pin 31): Port 2 Output Voltage Monitor. See OUT4.

SENSE1 (Pin 32): Port 1 Current Sense Input. See SENSE4.

GATE1 (Pin 33): Port 1 Gate Drive. See GATE 4.

OUT1 (Pin 34): Port 1 Output Voltage Monitor. See OUT4.

**AUTO (Pin 35):** Auto Mode Input. Auto mode is intended to allow the LTC4258 to detect and power up a PD even if there is no host controller present on the  $I^2C$  bus. The voltage of the AUTO pin determines the state of the internal registers when the LTC4258 is reset or comes out of  $V_{DD}$  UVLO (see the Register map in Table 1). The states of these register bits can subsequently be changed via the  $I^2C$  interface if desired. The real-time state of the AUTO pin can be read at bit 0 in the Pin Status register (11h). Pull AUTO high or low with  $\leq$ 10k or tie to  $V_{DD}$  or DGND.

**NC (Pin 36):** No Internal Connection.

## TABLE 1. REGISTER MAP

| ADDR       | ADDRESS REGISTER NAME            | R/W | PORT   | BIT 7                   | BIT 6               | BIT 5                   | BIT 4                | BIT 3                                                                                                     | BIT 2                     | BIT 1                     | BITO                      | RESET STATE                                                       | RESET STATE                                                       |

|------------|----------------------------------|-----|--------|-------------------------|---------------------|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| Interrupts | upts                             |     |        |                         |                     |                         |                      |                                                                                                           |                           |                           |                           | Auto Pin Low                                                      | Auto Pin High                                                     |

| 00h        | Interrupt                        | RO  | Global | Supply Event            | tstart Fault        | t <sub>ICUT</sub> Fault | Class Complete       | Detect Complete                                                                                           | Disconnect                | Pwr Good Event            | Pwr Enable Event          | 1000,0000                                                         | 1000,0000                                                         |

| 01h        | Int Mask                         | R/W | Global | Mask 7                  | Mask 6              | Mask 5                  | Mask 4               | Mask 3                                                                                                    | Mask 2                    | Mask 1                    | Mask 0                    | 1000,0000                                                         | 1110,0100                                                         |

| Events     | 8                                |     |        |                         |                     |                         |                      |                                                                                                           |                           |                           |                           |                                                                   |                                                                   |

| 02h        | 02h Power Event                  | R0  | 4321   | Pwr Good                | Pwr Good            | Pwr Good                | Pwr Good             | Pwr Enable                                                                                                | Pwr Enable                | Pwr Enable                | Pwr Enable                | 0000,0000                                                         | 0000,0000                                                         |

| 03h        | 03h Power Event CoR              | CoR |        | Change 4                | Change 3            | Change 2                | Change 1             | Change 4                                                                                                  | Change 3                  | Change 2                  | Change 1                  |                                                                   |                                                                   |

| 04h        | 04h Detect Event                 | R0  | 4321   | Class Complete 4        | e 3                 | Class Complete 2        | Class Complete 1     | Class Complete 2 Class Complete 1 Detect Complete 4 Detect Complete 3 Detect Complete 2 Detect Complete 1 | Detect Complete 3         | Detect Complete 2         | Detect Complete 1         | 0000,0000                                                         | 0000,0000                                                         |

| 05h        | 05h Detect Event CoR             | CoR |        |                         |                     |                         |                      |                                                                                                           |                           |                           |                           |                                                                   |                                                                   |

| 190        | Fault Event                      | RO  | 4321   | Disconnect 4            | Disconnect 3        | Disconnect 2            | Disconnect 1         | t <sub>ICUT</sub> Fault 4                                                                                 | t <sub>ICUT</sub> Fault 3 | t <sub>ICUT</sub> Fault 2 | t <sub>ICUT</sub> Fault 1 | 0000,0000                                                         | 0000,0000                                                         |

| 07h        | 07h Fault Event CoR              | CoR |        |                         |                     |                         |                      |                                                                                                           |                           |                           |                           |                                                                   |                                                                   |

| 08h        | 08h tstarr Event                 | R0  | 4321   | Reserved                | Reserved            | Reserved                | Reserved             | tSTART Fault 4                                                                                            | tSTART Fault 3            | tSTART Fault 2            | tSTART Fault 1            | 0000,0000                                                         | 0000,0000                                                         |

| 09h        | 09h t <sub>START</sub> Event CoR | CoR |        |                         |                     |                         |                      |                                                                                                           |                           |                           |                           |                                                                   |                                                                   |

| 0Ah        | 0Ah Supply Event                 | RO  | 4321   | Over Temp               | Reserved            | V <sub>DD</sub> UVLO    | V <sub>EE</sub> UVLO | Reserved                                                                                                  | Reserved                  | Reserved                  | Reserved                  | 0011,0000**                                                       | 0011,0000**                                                       |

| 0Bh        | 0Bh Supply Event CoR             | CoR |        |                         |                     |                         |                      |                                                                                                           |                           |                           |                           |                                                                   |                                                                   |

| Status     |                                  |     |        |                         |                     |                         |                      |                                                                                                           |                           |                           |                           |                                                                   |                                                                   |

| 0Ch        | Port 1 Status                    | B0  | -      | Reserved                | Class Status 2      | Class Status 1          | Class Status 0       | Reserved                                                                                                  | Detect Status 2           | Detect Status 1           | Detect Status 0           | 0000,0000                                                         | 0000,0000                                                         |

| 0Dh        | 0Dh Port 2 Status                | RO  | 2      | Reserved                | Class Status 2      | Class Status 1          | Class Status 0       | Reserved                                                                                                  | Detect Status 2           | Detect Status 1           | Detect Status 0           | 0000,0000                                                         | 0000,0000                                                         |

| 0Eh        | 0Eh Port 3 Status                | RO  | 3      | Reserved                | Class Status 2      | Class Status 1          | Class Status 0       | Reserved                                                                                                  | Detect Status 2           | Detect Status 1           | Detect Status 0           | 0000,0000                                                         | 0000,0000                                                         |

| 0Fh        | Port 4 Status                    | RO  | 4      | Reserved                | Class Status 2      | Class Status 1          | Class Status 0       | Reserved                                                                                                  | Detect Status 2           | Detect Status 1           | Detect Status 0           | 0000,0000                                                         | 0000,0000                                                         |

| 10h        | 10h Power Status                 | RO  | 4321   | Power Good 4            | Power Good 3        | Power Good 2            | Power Good 1         | Power Enable 4                                                                                            | Power Enable 3            | Power Enable 2            | Power Enable 1            | 0000,0000                                                         | 0000,0000                                                         |

| 11h        | 11h Pin Status                   | RO  | Global | Reserved                | Reserved            | AD3 Pin Status          | AD2 Pin Status       | AD1 Pin Status                                                                                            | AD0 Pin Status            | Reserved                  | Auto Pin Status           | 00A <sub>3</sub> A <sub>2</sub> ,A <sub>1</sub> A <sub>0</sub> 00 | 00A <sub>3</sub> A <sub>2</sub> ,A <sub>1</sub> A <sub>0</sub> 01 |

| Config     | Configuration                    |     |        |                         |                     |                         |                      |                                                                                                           |                           |                           |                           |                                                                   |                                                                   |

| 12h        | Operating Mode                   | R/W | 4321   | Port 4 Mode 1           | Port 4 Mode 0       | Port 3 Mode 1           | Port 3 Mode 0        | Port 2 Mode 1                                                                                             | Port 2 Mode 0             | Port 1 Mode 1             | Port 1 Mode 0             | 0000,0000                                                         | 1111,1111                                                         |

| 13h        | 13h Disconnect Enable            | R/W | 4321   | Reserved                | Reserved            | Reserved                | Reserved             | DC Discon En 4                                                                                            | DC Discon En 3            | DC Discon En 2            | DC Discon En 1            | 0000,0000                                                         | 0000,1111                                                         |

| 14h        | 14h Detect/Class Enable          | R/W | 4321   | Class Enable 4          | Class Enable 3      | Class Enable 2          | Class Enable 1       | Detect Enable 4                                                                                           | Detect Enable 3           | Detect Enable 2           | Detect Enable 1           | 0000,0000                                                         | 1111,1111                                                         |

| 15h        | 15h Reserved                     | R/W |        | Reserved                | Reserved            | Reserved                | Reserved             | Reserved                                                                                                  | Reserved                  | Reserved                  | Reserved                  | 0000,0000                                                         | 0000,0000                                                         |

| 16h        | 16h Timing Config                | R/W | Global | Reserved                | Reserved            | tstart1                 | tstarto              | t <sub>ICUT1</sub>                                                                                        | tıсито                    | toisi                     | t <sub>DISO</sub>         | 0000,0000                                                         | 0000,0000                                                         |

| 17h        | 17h Misc Config                  | R/W | Global | Interrupt Pin<br>Enable | Reserved            | Reserved                | Reserved             | Reserved                                                                                                  | Reserved                  | Reserved                  | Reserved                  | 1000,0000                                                         | 1000,0000                                                         |

| Pushb      | Pushbuttons                      |     |        |                         |                     |                         |                      |                                                                                                           |                           |                           |                           |                                                                   |                                                                   |

| 18h        | 18h Det/Class Restart PB         | MO  | 4321   | Restart Class 4         | Restart Class 3     | Restart Class 2         | Restart Class 1      | Restart Detect 4                                                                                          | Restart Detect 3          | Restart Detect 2          | Restart Detect 1          | 0000,0000                                                         | 0000,0000                                                         |

| 19h        | 19h Power Enable PB              | WO  | 4321   | Power Off 4             | Power Off 3         | Power Off 2             | Power Off 1          | Power On 4                                                                                                | Power On 3                | Power On 2                | Power On 1                | 0000,0000                                                         | 0000,0000                                                         |

| 1Ah        | 1Ah Reset PB                     | WO  | Global | Clear All<br>Interrupts | Clear Interrupt Pin | Reserved                | Reset All            | Reset Port 4                                                                                              | Reset Port 3              | Reset Port 2              | Reset Port 1              | 0000,0000                                                         | 0000,0000                                                         |

\*\* the start-up state of the VEE UVLO and Osc Fail bits depend on the order in which the V<sub>DD</sub> and V<sub>EE</sub> supplies are brought up

Key:

RO = Read Only

RW = Read/Write

COR = Clear on Read

WO = Write Only

| Encoding | Ďi,                       |        |                       |        |                   |                                                |

|----------|---------------------------|--------|-----------------------|--------|-------------------|------------------------------------------------|

| CLASS    | LASS STATUS               | DETECT | DETECT STATUS         | MODE B | MODE BIT ENCODING |                                                |

| 000      | Class Status Unknown      | 000    | Detect Status Unknown | 00     | Shutdown          | 00 Shutdown Power Off, Detection and Class Off |

| 100      | Class 1                   | 100    | Short Circuit (<1V)   | 10     | Manual            | Will Not Advance Between States                |

| 010      | Class 2                   | 010    | Reserved              | 10     | Semiauto          | Detect and Class But Wait to Turn On Power     |

| 011      | Class 3                   | 011    | RLOW                  | =      | Auto              | Detect, Class and Power Automatically          |

| 100      | Class 4                   | 100    | Detect Good           |        |                   |                                                |

| 101      | Undefined—Read as Class 0 | 101    | RHIGH                 |        |                   |                                                |

| 110      | Class 0                   | 110    | Open Circuit          |        |                   |                                                |

| =        | Overcurrent               | =      | Reserved              |        |                   |                                                |

## REGISTER FUNCTIONS

#### **Interrupt Registers**

Interrupt (Address 00h): Interrupt Register, Read Only. A transition to logical 1 of any bit in this register will assert the INT pin (Pin 3) if the corresponding bit in the Int Mask register is set. Each bit is the logical OR of the corresponding bits in the Event registers. The Interrupt register is Read Only and its bits cannot be cleared directly. To clear a bit in the Interrupt register, clear the corresponding bits in the appropriate Status or Event registers or set bit 7 in the Reset Pushbutton register (1Ah).

Int Mask (Address 01h): Interrupt Mask, Read/Write. A logic 1 in any bit of the Int Mask register allows the corresponding Interrupt register bit to assert the INT pin if it is set. A logic 0 in any bit of the Int Mask register prevents the corresponding Interrupt bit from affecting the INT pin. The actual Interrupt register bits are unaffected by the state of the Int Mask register.

#### **Event Registers**

Power Event (Address 02h): Power Event Register, Read Only. The lower four bits in this register indicate that the corresponding port Power Enable status bit has changed; the logical OR of these four bits appears in the Interrupt register as the Pwr Enable Event bit. The upper four bits indicate that the corresponding port Power Good status bit has changed; the logical OR of these four bits appears in the Interrupt register as the Pwr Good Event bit. The Power Event bits latch high and will remain high until cleared by reading from address 03h.

**Power Event CoR (Address 03h):** Power Event Register, Clear on Read. Read this address to clear the Power Event register. Address 03h returns the same data as address 02h and reading address 03h clears all bits at both addresses.

**Detect Event (Address 04h):** Detect Event Register, Read Only. The lower four bits in this register indicate that at least one detection cycle for the corresponding port has completed; the logical OR of these four bits appears in the Interrupt register as the Detect Complete bit. The upper four bits indicate that at least one classification cycle for the corresponding port has completed; the logical OR of these four bits appears in the Interrupt register as the Class Complete bit. In Manual mode, this register indicates that the requested detection/classification cycle has completed and

the LTC4258 is awaiting further instructions. In Semiauto or Auto modes, these bits indicate that the Detect Status and Class Status bits in the Port Status registers are valid. The Detect Event bits latch high and will remain high until cleared by reading from address 05h.

**Detect Event CoR (Address 05h):** Detect Event Register, Clear on Read. Read this address to clear the Detect Event register. Address 05h returns the same data as address 04h, and reading address 05h clears all bits at both addresses.

Fault Event (Address 06h): Fault Event Register, Read Only. The lower four bits in this register indicate that a  $t_{ICUT}$  fault has occurred at the corresponding port; the logical OR of these four bits appears in the Interrupt register as the  $t_{ICUT}$  Fault bit. The upper four bits indicate that a Disconnect event has occurred at the corresponding port; the logical OR of these four bits appears in the Interrupt register as the Disconnect bit. The Fault Event bits latch high and will remain high until cleared by reading from address 07h.

**Fault Event CoR (Address 07h):** Fault Event Register, Clear on Read. Read this address to clear the Fault Event register. Address 07h returns the same data as address 06h and reading address 07h clears all bits at both addresses.

**t**<sub>START</sub> **Event (Address 08h):**  $t_{START}$  Event Register, Read Only. The lower four bits in this register indicate that a  $t_{START}$  fault has occurred at the corresponding port; the logical OR of these four bits appears in the Interrupt register as the  $t_{START}$  Fault bit. The  $t_{START}$  Event bits latch high and will remain high until cleared by reading from address 09h. The upper four bits in this register are reserved and will always read as 0.

**t<sub>START</sub> Event CoR (Address 09h):** t<sub>START</sub> Event Register, Clear on Read. Read this address to clear the Fault Event register. Address 09h returns the same data as address 08h and reading address 09h clears all bits at both addresses.

**Supply Event (Address 0Ah):** Supply Event Register, Read Only. Bit 4 indicates that  $V_{EE}$  has dropped below the  $V_{EE}$  UVLO level (typically -28V). Bit 5 signals that the  $V_{DD}$  supply has dropped below the  $V_{DD}$  UVLO threshold. Bit 7 indicates that the LTC4258 die temperature has exceeded its thermal shutdown limit (see Note 4 under Electrical Characteristics). The logical OR of bits 4, 5 and 7 appears in the Inter-

LINEAR

## REGISTER FUNCTIONS

rupt register as the Supply Fault bit. The remaining bits in the register are reserved and will always read as 0. The Supply Event bits latch high and will remain high until cleared by reading from address 0Bh.

**Supply Event CoR (Address OBh):** Supply Event Register, Clear on Read. Read this address to clear the Fault Event register. Address OBh returns the same data as address OAh, and reading address OBh clears all bits at both addresses.

#### **Status Registers**

Port 1 Status (Address OCh): Port 1 Status Register, Read Only. This register reports the most recent detection and classification results for port 1. Bits 0-2 report the status of the most recent detection attempt at the port and bits 4-6 report the status of the most recent classification attempt at the port. If power is on, these bits report the detection/classification status present just before power was turned on. If power is turned off at the port for any reason, all bits in this register will be cleared. See Table 1 for detection and classification status bit encoding.

**Port 2 Status (Address 0Dh):** Port 2 Status Register, Read Only. See Port 1 Status.

**Port 3 Status (Address 0Eh):** Port 3 Status Register, Read Only. See Port 1 Status.

**Port 4 Status (Address 0Fh):** Port 4 Status Register, Read Only. See Port 1 Status.

**Power Status (Address 10h):** Power Status Register, Read Only. The lower four bits in this register report the switch on/off state for the corresponding ports. The upper four bits (the power good bits) indicate that the drop across the power switch and sense resistor for the corresponding ports is less than 2V (typ) and power start-up is complete. The power good bits are latched high and are only cleared when a port is turned off or the LTC4258 is reset.

**Pin Status (Address 11h):** External Pin Status, Read Only. This register reports the real time status of the AUTO (Pin 35) and ADO-AD3 (Pins 7-10) digital input pins. The logic state of the AUTO pin appears at bit 0 and the ADO-AD3 pins at bits 2-5. The remaining bits are reserved and will read as 0. AUTO affects the initial states of some of the

LTC4258 configuration registers at start-up but has no effect after start-up and can be used as a general purpose input if desired, as long as it is guaranteed to be in the appropriate state at start-up.

#### **Configuration Registers**

**Operating Mode (Address 12h):** Operating Mode Configuration, Read/Write. This register contains the mode bits for each of the four ports in the LTC4258. See Table 1 for mode bit encoding. At power-up, all bits in this register will be set to the logic state of the AUTO pin (Pin 35). See Operating Modes in the Applications Information section.

**Disconnect Enable (Address 13h):** Disconnect Enable Register, Read/Write. The lower four bits of this register enable or disable DC disconnect detection circuitry at the corresponding port. If the DC Discon Enable bit is set the port circuitry will turn off power if the current draw at the portfalls below  $I_{MIN}$  for more than  $t_{DIS}.$   $I_{MIN}$  is equal to  $V_{MIN}/R_S$ , where  $R_S$  is the sense resistor and should be  $0.5\Omega$  for IEEE 802.3af compliance. If the bit is clear the port will not remove power due to low current.

**Detect/Class Enable (Address 14h):** Detection and Classification Enable, Read/Write. The lower four bits of this register enable the detection circuitry at the corresponding port if that port is in Auto or Semiauto mode. The upper four bits enable the classification circuitry at the corresponding port if that port is in Auto or Semiauto mode. In manual mode, setting a bit in this register will cause the LTC4258 to perform one classification or detection cycle on the corresponding port. Writing to the Detect/Class Restart PB (18h) has the same effect without disturbing the Detect/Class Enable bits for other ports.

**Timing Config (Address 16h):** Global Timing Configuration, Read/Write. Bits 0-1 program  $t_{DIS}$ , the time duration before a port is automatically tuned off after the PD is removed. The LTC4258 can be programmed to monitor whether port current is below  $l_{MIN}$  (DC connect) or port impedance is high (AC disconnect). Bits 2-3 program  $t_{ICUT}$ , the time during which a port's current can exceed  $l_{CUT}$  without it being turned off. If the current is still above  $l_{CUT}$  after  $t_{ICUT}$ , the LTC4258 will indicate a  $t_{ICUT}$  fault and turn the port off. Bits

## REGISTER FUNCTIONS

4-5 program  $t_{START}$ , the time duration before an overcurrent condition during port power-on is considered a  $t_{START}$  fault and the port is turned off. Note that using the  $t_{ICUT}$  and  $t_{START}$  times other than the default is not compliant with IEEE 802.3af and may double or quadruple the energy dissipated by the external MOSFETs during fault conditions. Bits 6-7 are reserved and should be read/written as 0. See Electrical Characteristics for timer bit encoding. Also see the Applications Information for descriptions of  $t_{START}$ ,  $t_{ICUT}$  and DC disconnect timing.

**Misc Config (Address 17h):** Miscellaneous Configuration, Read/Write. Setting bit 7 enables the INT pin. If this bit is reset, the LTC4258 will not pull down the INT pin in any condition nor will it respond to the Alert Response Address. This bit is set by default.

#### **Pushbutton Registers**

**Note Regarding Pushbutton Registers:** "Pushbutton" registers are specialized registers that trigger an event when a 1 is written to a bit; writing a 0 to a bit will do nothing. Unlike a standard read/write register, where setting a single bit involves reading the register to determine its status, setting the appropriate bit in software and writing back the entire register, a pushbutton register allows a single bit to be written without knowing or affecting the status of the other bits in the register. Pushbutton registers are write-only and will return 00h if read.

**Det/Class Restart PB (Address 18h):** Detection/Classification Restart Pushbutton Register, Write Only. Writing a 1 to any bit in this register will start or restart a single detection or classification cycle at the corresponding port in Manual mode. It can also be used to set the corresponding bits in the Detect/Class Enable register (address 14h) for ports in auto or semiauto mode. The lower 4 bits affect detection on each port while the upper 4 bits affect classification.

Power Enable PB (Address 19h): Power Enable Pushbutton Register, Write Only. The lower four bits of this register set the Power Enable bit in the corresponding Port Status register; the upper four bits clear the corresponding Power Enable bit. Setting or clearing the Power Enable bits via this register will turn on or off the power in any mode except shutdown, regardless of the state of detection or classification. Note that t<sub>ICUT</sub>, t<sub>START</sub> and disconnect events (if enabled) will still turn off power if they occur.

The Power Enable bit cannot be set if the port has turned off due to a  $t_{ICUT}$  or  $t_{START}$  fault and the  $t_{ICUT}$  timer has not yet counted back to zero. See Applications Information for more information on  $t_{ICUT}$  timing.

Clearing the Power Enable bits with this register also clears the detect and fault event bits, the Port Status register, and the Detection and Classification Enable bits for the affected port(s).

Reset PB (Address 1Ah): Reset Pushbutton, Write Only. Bits 0-3 reset the corresponding port by clearing the power enable bit, the detect and fault event bits, the status register and the detection and classification enable bits for that port. Bit 4 returns the entire LTC4258 to the power-on reset state; all ports are turned off, the AUTO pin is reread and all registers are returned to their power-on defaults, except V<sub>DD</sub> UVLO, which remains cleared. Bit 5 is reserved; setting it has no effect. Setting bit 6 releases the Interrupt pin if it is asserted without affecting the Event registers or the Interrupt register. When the INT pin is released in this way, the condition causing the LTC4258 to pull the INT pin down must be removed before the LTC4258 will be able to pull INT down again. This can be done by reading and clearing the event registers or by writing a 1 into bit 7 of this register. Setting bit 7 releases the Interrupt pin, clears all the Event registers and clears all the bits in the Interrupt register.

#### **OVERVIEW**

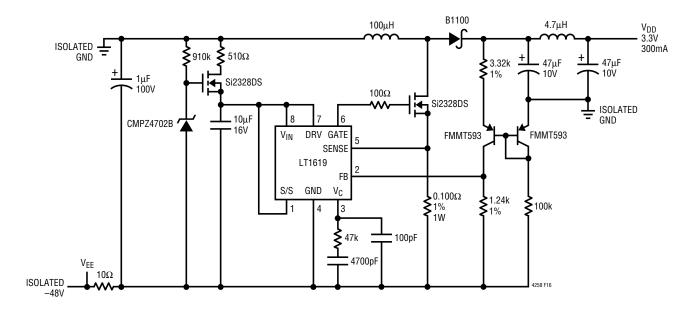

Over the years, twisted-pair Ethernet has become the most commonly used method for local area networking. The IEEE 802.3 group, the originator of the Ethernet standard, has defined an extension to the standard, known as 802.3af, which allows DC power to be delivered simultaneously over the same cable used for data communication. This promises a whole new class of Ethernet devices. including IP telephones, wireless access points, and PDA charging stations, which do not require additional AC wiring or external power transformers, a.k.a. "wall warts." With about 13W of power available, small data devices can be powered by their Ethernet connections, free from AC wall outlets. Sophisticated detection and power monitoring techniques prevent damage to legacy data-only devices, while still supplying power to newer. Ethernetpowered devices over the twisted-pair cable.

A device that supplies power is called Power Sourcing Equipment (PSE); a device that draws power from the wire is called a Powered Device (PD). A PSE is typically an Ethernet switch, router, hub, or other network switching

equipment that is commonly found in the wiring closets where cables converge. PDs can take many forms: digital IP telephones, wireless network access points, PDA or notebook computer docking stations, cell phone chargers, and HVAC thermostats are examples of devices that can draw power from the network.

A PSE is required to provide a nominal 48V DC between either the signal pairs or the spare pairs (but not both) as shown in Figure 10. The power is applied as a voltage between two of the pairs, typically by powering the centertaps of the isolation transformers used to couple the differential data signals to the wire. Since Ethernet data is transformer coupled at both ends and is sent differentially, a voltage difference between the transmit pairs and the receive pairs does not affect the data. A 10base-T/100base-TX Ethernet connection only uses 2 of the 4 pairs in the cable. The unused or spare pairs can be powered directly, as shown in Figure 10, without affecting the data. However, 1000base-T uses all 4 pairs and power must be connected to the transformer center taps if compatibility with 1000base-T is required.

Figure 10. System Diagram

The LTC4258 provides a complete solution for detection and powering of PD devices in an IEEE 802.3af compliant system. The LTC4258 consists of four independent ports, each with the ability to detect, classify, and provide isolated –48V power to a PD device connected to it. The LTC4258 senses removal of a PD with IEEE 802.3af compliant AC or DC methods and turns off –48V power when the PD is removed. An internal control circuit takes care of system configuration and timing, and uses an I<sup>2</sup>C interface to communicate with the host system.

#### **OPERATING MODES**

Each LTC4258 port can operate in one of four modes: Manual, Semiauto, Auto or Shutdown. The operating mode for a port is set by the appropriate bits in the Operating Mode register. The LTC4258 will power up with all ports in Shutdown mode if the external AUTO pin is tied low; if AUTO is high, all ports will wake up in Auto mode. The operating mode can be changed at any time via the I<sup>2</sup>C interface, regardless of the state of the AUTO pin.

- In Manual mode, a port will wait for instructions from the host system before taking any action. It will run single detection or classification cycles when commanded, and will report results in the Port Status registers. When the host system decides it is time to turn on or off power to a port, it can do so by setting the appropriate Power On/Off bits in the Power Enable PB register regardless of the current status of detection or classification.

- In Semiauto mode, the port will repeatedly attempt to detect and classify a PD device attached to the link. It will report this information in its Port Status register, and wait for the host system to set the appropriate Power On bit in the Power Enable PB register before applying power to the port.

- In Auto mode, the port will detect and classify a PD device connected to it, then immediately turn on the power if detection was successful regardless of the result of classification.

- In Shutdown mode, the port is disabled and will not detect or power a PD. Also, the detect and fault event bits, status bits and enable bits for the port are reset to zero.

Regardless of which mode it is in, the LTC4258 will remove power automatically from any port that generates a  $t_{START}$  or  $t_{ICUT}$  overcurrent fault event (see  $t_{ICUT}$  Timing and  $t_{START}$  Timing sections). It will also automatically remove power from any port that generates a disconnect event if the appropriate Disconnect Enable bit is set in the Disconnect Enable register. The host controller may also remove power at any time by setting the appropriate Power Off bit in the Power Enable PB register.

#### **Power-On RESET**

At turn-on or any time the LTC4258 is reset (either by pulling the RESET pin low or writing to the global Reset All bit), all the ports turn off and all internal registers go to a predefined state, shown in Table 1.

Several of the registers assume different states based on the state of the AUTO pin at reset. The default states with AUTO high allow the LTC4258 to detect and power up a PD in Automatic mode, even if nothing is connected to the  $I^2C$  interface.

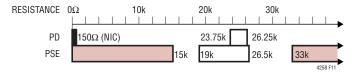

#### SIGNATURE DETECTION

The IEEE defines a specific pair-to-pair PD signature resistance that identifies a device that can accept Power over Ethernet in accordance with the 802.3af specification. When the port voltage is below 10V, an 802.3af compliant PD will have a 25k signature resistance. Figure 11 illustrates the relationship between the PD signature resistance (white box from 23.75k to 26.25k) and required resistance ranges the PSE must accept (white box) and reject (gray boxes). According to the 802.3af specification, the PSE may or may not accept resistances in the two ranges of 15k to 19k and 26.5k to 33k. Note that the black box in Figure 11 represents the 150 $\Omega$  pair-to-pair termination used in legacy 802.3 devices like a computer's network interface card (NIC) that cannot accept power.

Figure 11. IEEE 802.3af Signature Resistance Ranges

The LTC4258 checks for the signature resistance by forcing two test currents on the port (via the DETECT*n* pins) in sequence and measuring the resulting voltages. It then subtracts the two V-I points to determine the resistive slope while removing voltage offset caused by any series diodes or current offset caused by leakage at the port (see Figure 12). The LTC4258 will typically accept any PD resistance between 17k and 29k as a valid PD and report Detect Good (100 binary) in the Detect Status bits (bits 2 through 0) of the corresponding Port Status register. Values outside this range, including open and short circuits, are also reported in the Detect Status bits. Refer to Table 1 for a complete decoding of the Detect Status bits.

The first test point is taken by forcing a test current into the port, waiting a short time to allow the line to settle and measuring the resulting voltage. This result is stored and the second current is applied to the port, allowed to settle and the voltage measured. Each point takes 100ms to measure, and an entire detection cycle takes 200ms.

Figure 12. PD Detection

The LTC4258 will not report Detect Good if the PD has more than  $5\mu F$  in parallel with its signature resistor.